Laporan Akhir Modul 3 Percobaan 1

2. Alat dan Bahan

[Kembali]

1. IC 74LS112

2. Logic Probe

Logic Probe dijadikan sebagai hasil keluaran atau output

3. SPDT

SPDT adalah singkatan dari Single Pole Double Throw.

Switch jenis ini dapat menghubungkan dan memutuskan satu sambungan arus listrik

pada dua arah sambungan.

3. Rangkaian Simulasi

[Kembali]

Percobaan 1 Asynchronous Binary Counter 4 bit dengan 4 J-K flipflop.

1. Rangkai rangkaian seperti gambar dibawah ini.

Rangkaian percobaan Asynchronous Binary

Counter 4 bit

Rangkaian percobaan Asynchronous Binary

Counter 4 bit

4. Prinsip Kerja Rangkaian

[Kembali]

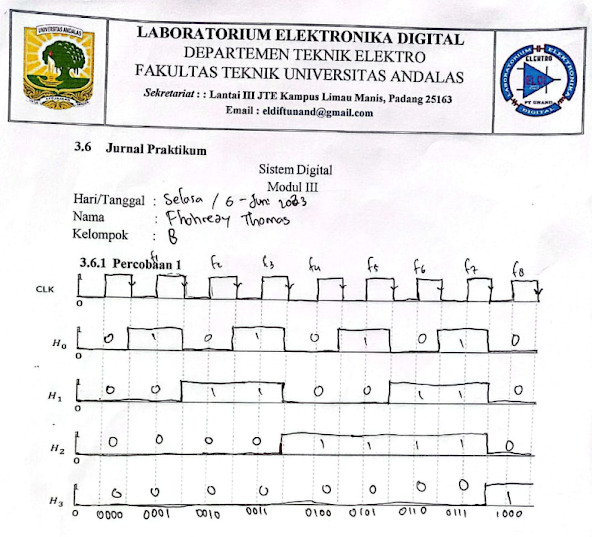

Pada percobaan 1, switch SPDT terhubung pada power, sehingga keluarannya 1, sedangkan IC 74LS112 pada kaki RS-nya merupakan aktif LOW. Sehingga utk keluarannya dipengaruhi oleh clock. Pada percobaan 1 ini merupakan counter asinkronus, ditandai dengan input clock pada flip-flopnya berasal dari keluaran output flip-flop sebelumnya. Pada counter ini keluarannya terlambat atau terdapat delay atau berubah saat kondisi fall time. Sehingga output masing-masing flip-flop yang digunakan akan bergulingan (berubah kondisi dan “0” ke “1”). Kaki MSB (output flip-flop terakhir dihubungkan ke kaki D pada decoder) dan kaki LSB (output flip-flop pertama dihubungkan ke kaki A pada decoder). Lalu, pada 7-segment bisa dilihat bahwa untuk keluarannya berurutan dari 0 ke 1, yang berarti counter up (menghitung ke atas).

5. Video Rangkaian

[Kembali]

6. Analisa

[Kembali]

Percobaan 1

1. analisa output percobaan berdasarkan DC yang digunakan

Jawab:

Output pada percobaan dipengaruhi oleh clock pada JK flip-flop yang pertama. Hal ini karena inputan S dan R dibuat tidak aktif, karena dihubungkan ke inputan 1. Karena S dan R aktif low, artinya akan aktif ketika inputan 0. Jika S aktif maka output akan berubah menjadi 1 untuk semua flip flop, namun jika R yang aktif maka output akan nol untuk semua flip-flop. Kemudian kaki J dan K dihubungkan ke inputan 1, artinya yang mempengaruhi output cuma clock. Inputan clock adalah aktif low artinya clocknya aktif ketika bernilai nol atau falltime.

2. Analisa sinyal output yang dikeluarkan jika klub kedua dan ketiga

Jawab:

Karena asyincronus counter, yang dipengaruhi oleh clock hanya JK flip-flop yang pertama. Sedangkan sinyal clock untuk flip-flop lainnya diambilkan dari output IC sebelumnya. Untuk sinyal output kedua, bisa dilihat pada timing diagram, outputnya akan menjadi 1 (berubah nilainya) jika output dari H0 (flip flop 1) berubah dari 1 menjadi p atau disebut falltime karena clocknya aktif low. Begitupun untuk flip-flop ke-3, outputnya pada timing diagram akan berubah nilai ketika nilai dari H1 (output JK flip flop 2) berubah dari 1 menjadi 0, karena clock JK flip flop 3 juga falltime.

7. Link Download

[Kembali]

Komentar

Posting Komentar