Laporan Akhir Modul 3 Percobaan 3

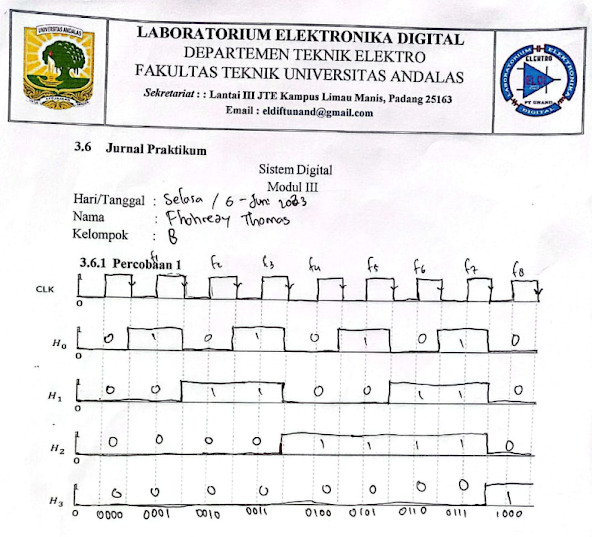

[KEMBALI KE MENU SEBELUMNYA] DAFTAR ISI 1. Jurnal 2. Alat dan Bahan 3. Rangkaian Simulasi 4. Prinsip Kerja Rangkaian 5. Video Rangkaian 6. Analisa 7. Link Download 1. Jurnal [Kembali] 2. Alat dan Bahan [Kembali] 1. IC 74193 2. IC 74192 3. Logic Probe Logic Probe dijadikan sebagai hasil keluaran atau output 4.SPDT SPDT adalah singkatan dari Single Pole Double Throw. Switch jenis ini dapat menghubungkan dan memutuskan satu sambungan arus listrik pada dua arah sambungan. 3. Rangkaian Simulasi [Kembali] Percobaan 3 Synchronous Binary Counter Gambar Rangkaian percobaan Synchronous binary counter percobaan 3a 1. Rangkaian Synchronous binary counter. 2. Variasikan switch pada rangkaian sesuai dengan kondisi yang ada pada jurnal. 3. Cek dan catat output yang terjadi melalui LED ke jurnal. 4. Matikan power supply dan rangkai rangkaian seperti gambar berikut dan ulangi perintah 2 dan 3. Pada praktikum kita menggunakan simulasi pa...